Hi everybody. My name is Gus Smith, and I'm a PhD candidate at the University of Washington's PLSE lab. Today I'm going to be talking about why we should generate compilers from hardware models.

First, let me shout out my coauthors in PLSE: Ben, Vishal, Andrew, Rene, and Zach, some of whom are in the audience today!

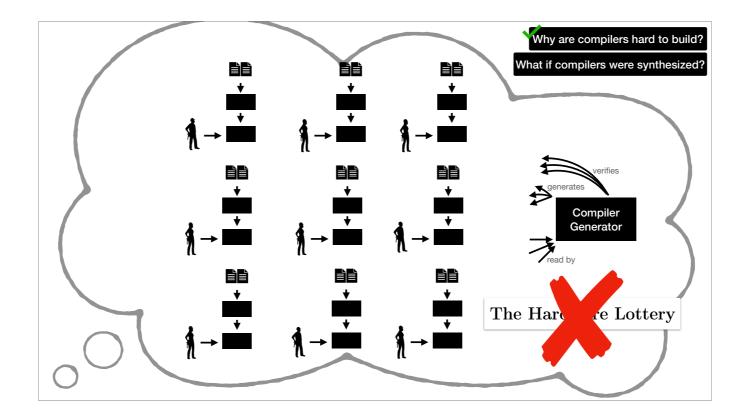

In 2020, Sara Hooker from Google Research released a paper titled the Hardware Lottery. The thesis of this paper is that

[build] ...

She argues that, for example, the current track of matrix-multiplication-based advances in machine learning are undeniably linked to the abundance of hardware for matrix multiplication, and that other research directions in machine learning are subsequently less likely to be successful.

The hardware lottery is a direct challenge to us in this room. By my reading, the takeaway for our community is that [build] new platforms (that is, new hardware and their associated compiler stack) should be easier to build, so that the best ideas win — not just the ideas with hardware on their side!

In this talk, I'm going to focus on what I know: [build] compilers. So, let's ask the question, [build] why *are* compilers so difficult

| The Hardware Lottery         |  |

|------------------------------|--|

| Sara Hooker                  |  |

| Google Research, Brain Team  |  |

| shooker@google.com 2020      |  |

| d compilers have a dispropor |  |

| 2020                         |  |

| d compilers have a dispropor |  |

| The Hardware Lottery                                  | 7  |

|-------------------------------------------------------|----|

| Sara Hooker                                           |    |

| Google Research, Brain Team<br>shooker@google.com     | 20 |

| compilers have a disprop<br>/hich research ideas suc  |    |

| our community: new platf<br>ck) should be easier to b |    |

|            | The Hardware Lottery                                                              |               |  |

|------------|-----------------------------------------------------------------------------------|---------------|--|

|            | Sara Hooker                                                                       |               |  |

|            | Google Research, Brain Team<br>shooker@google.com                                 | 20            |  |

|            |                                                                                   |               |  |

| deciding v | compilers have a disprop<br>which research ideas succ<br>our community: new platf | ceed or fail. |  |

|                                  | The Hardware Lottery                                                                             |             |

|----------------------------------|--------------------------------------------------------------------------------------------------|-------------|

|                                  | Sara Hooker                                                                                      |             |

|                                  | Google Research, Brain Team<br>shooker@google.com                                                |             |

|                                  | 2020                                                                                             |             |

|                                  | compilers have a disproportionate ro                                                             | le in       |

| deciding v                       | which research ideas succeed or fail.                                                            |             |

|                                  |                                                                                                  |             |

|                                  |                                                                                                  |             |

| Takeaway for c                   | our community: new platforms (hardw                                                              | are         |

| Takeaway for c<br>+ compiler sta | our community: new platforms (hardw<br>ck) should be easier to build, so that<br>best ideas win! | vare<br>the |

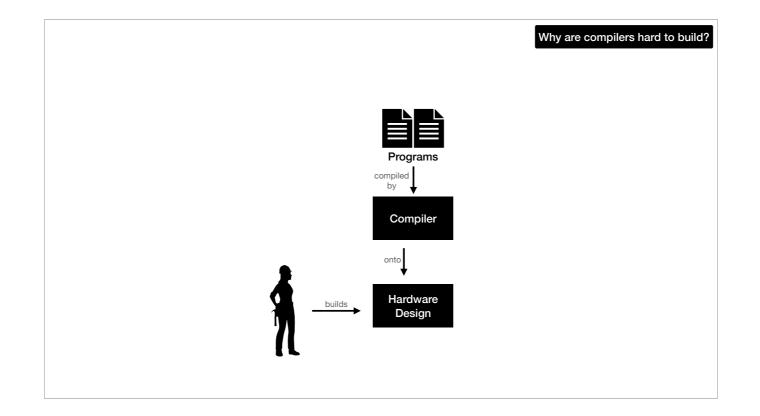

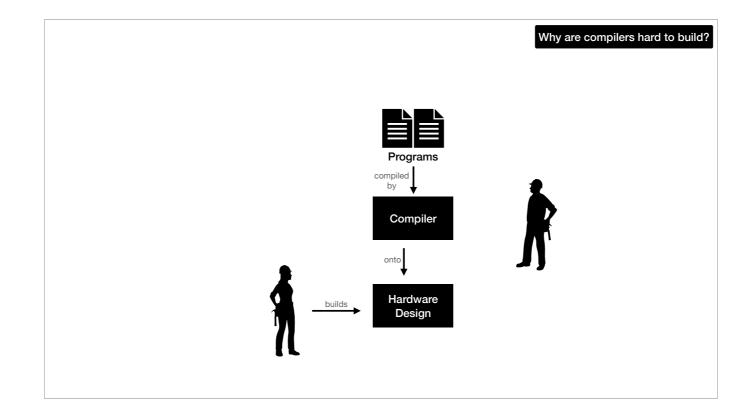

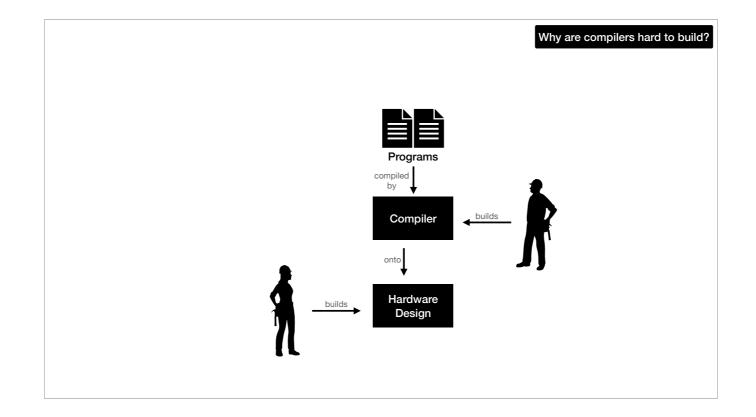

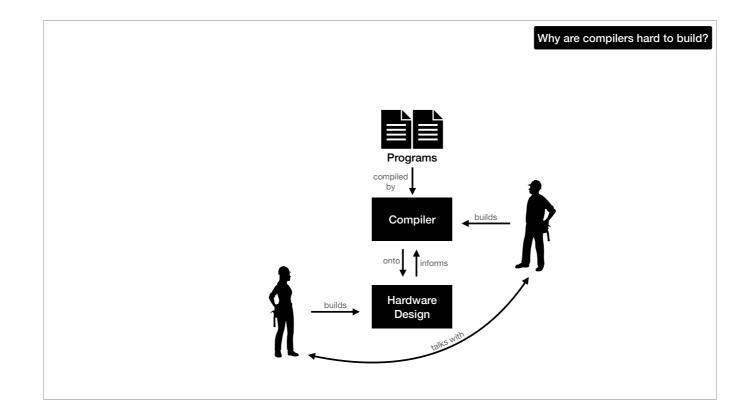

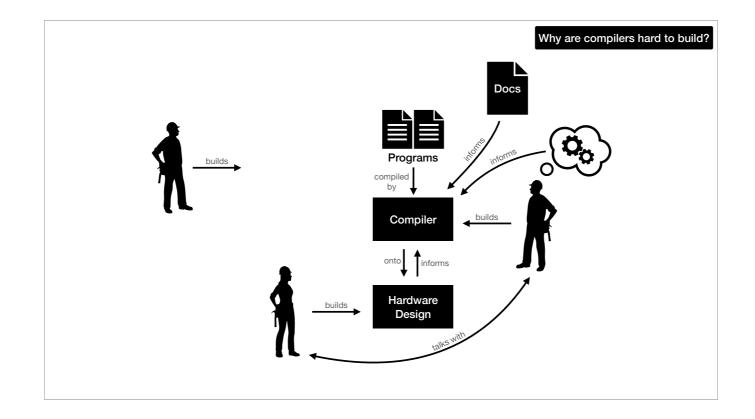

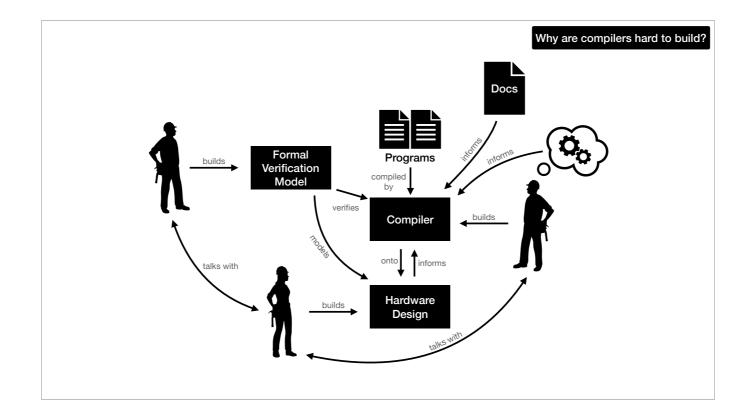

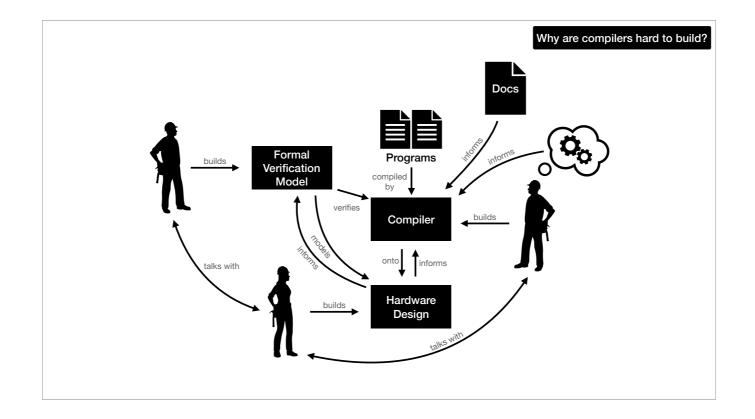

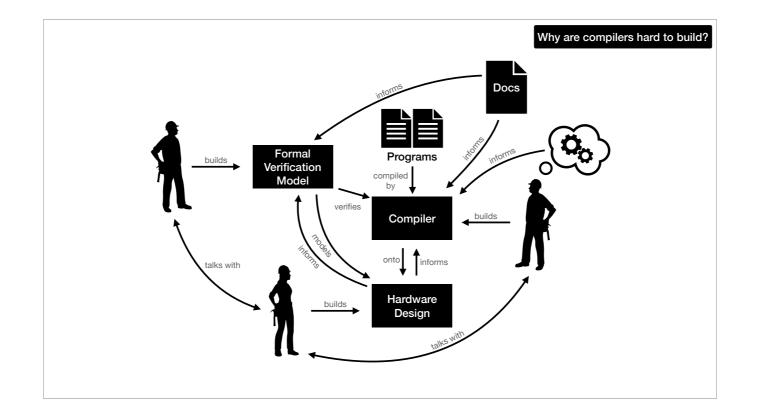

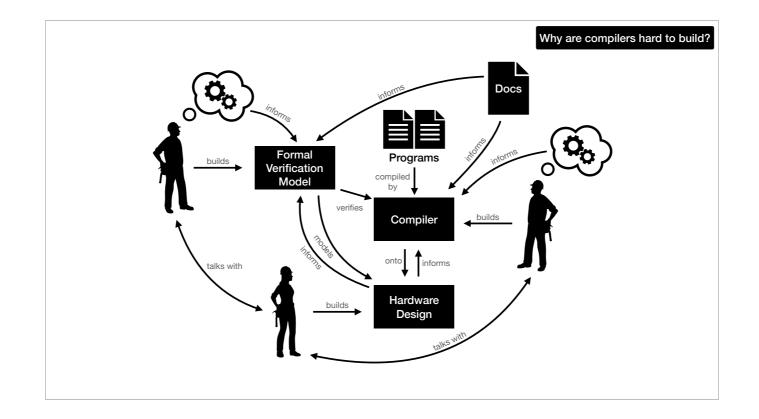

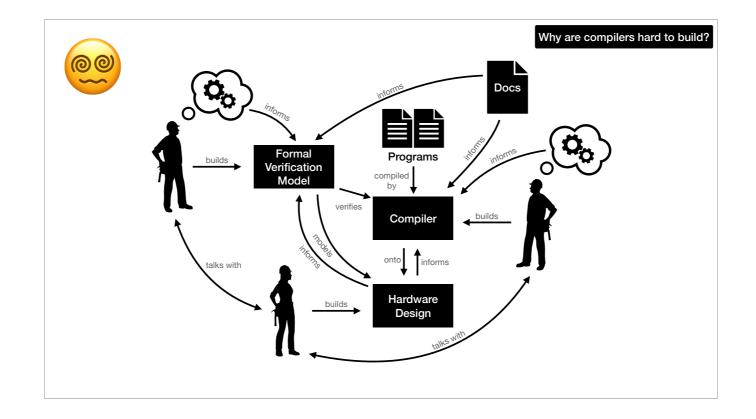

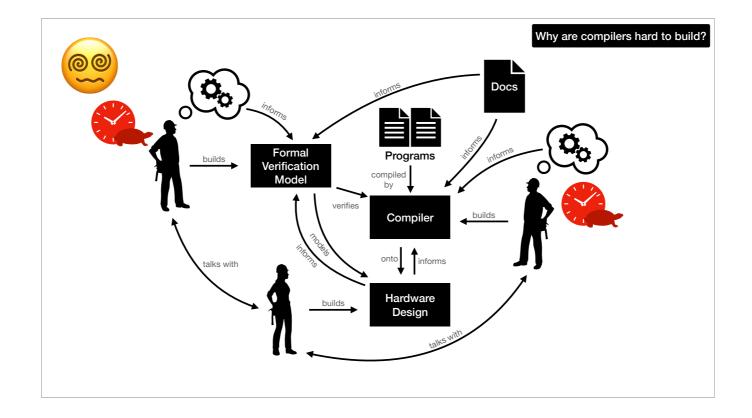

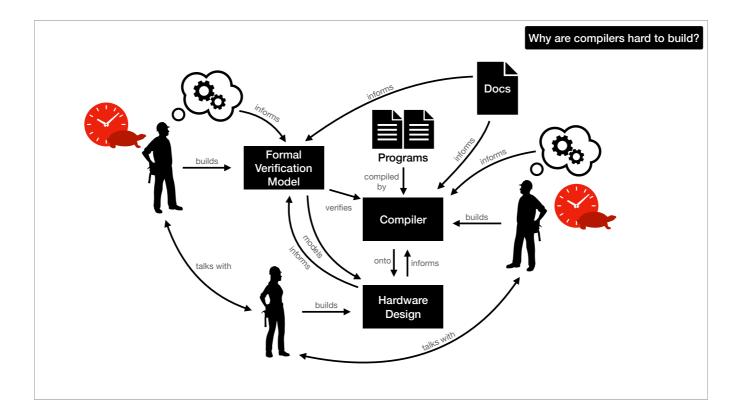

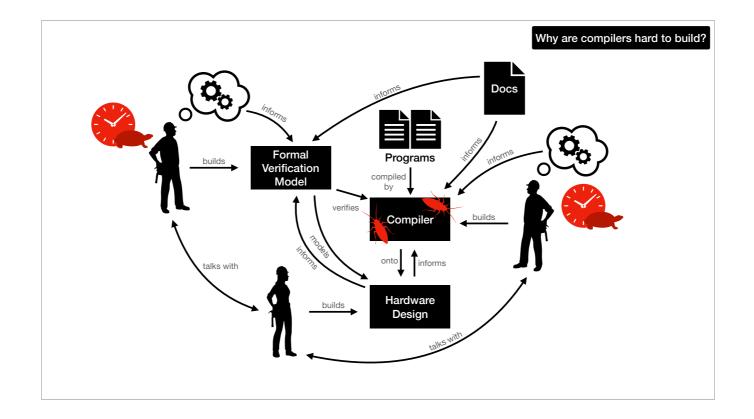

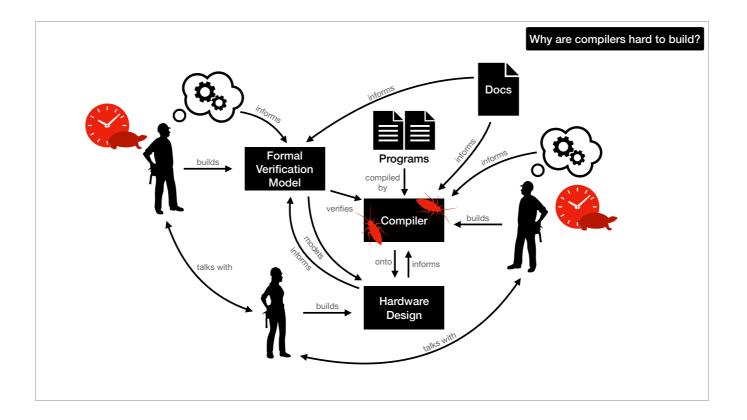

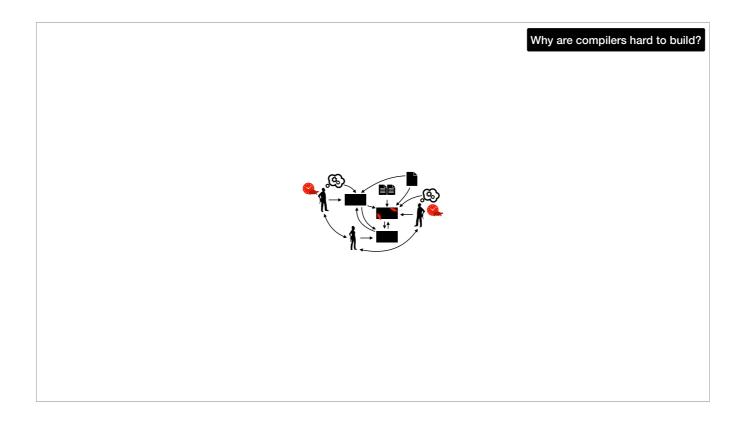

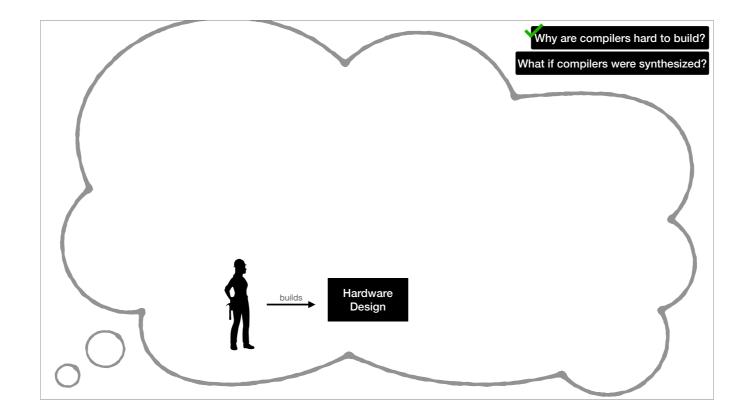

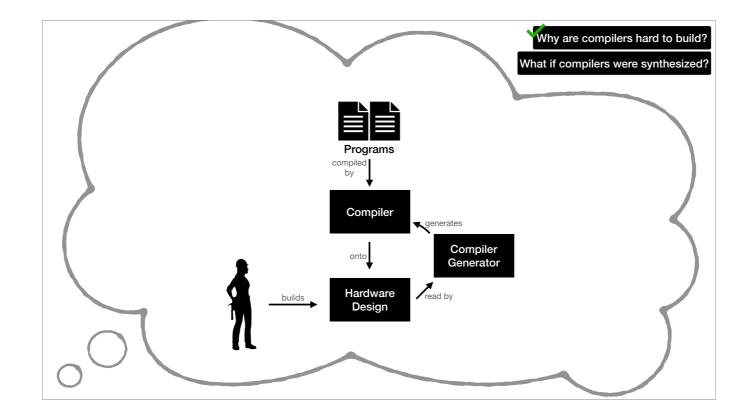

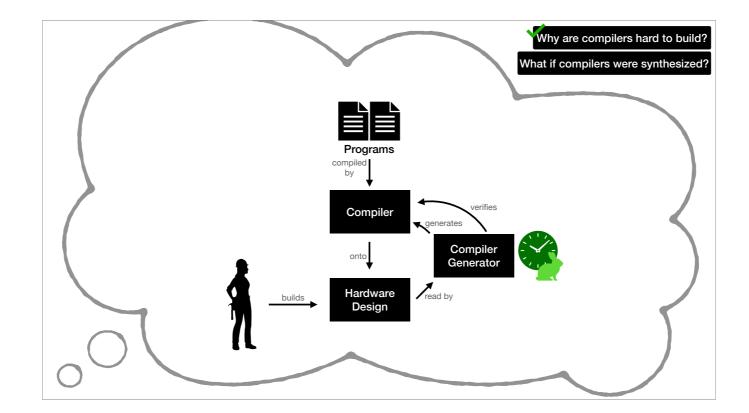

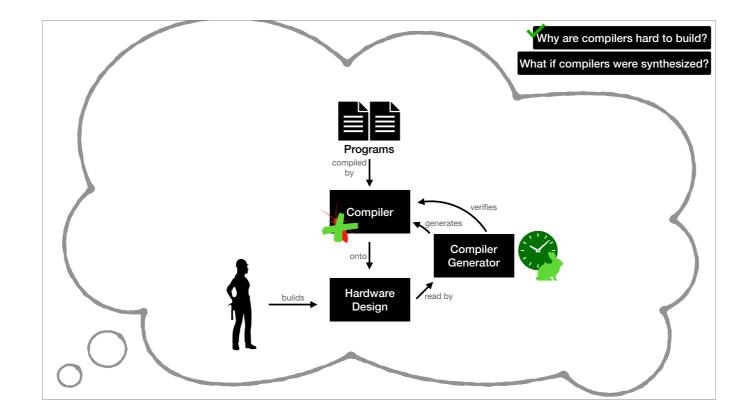

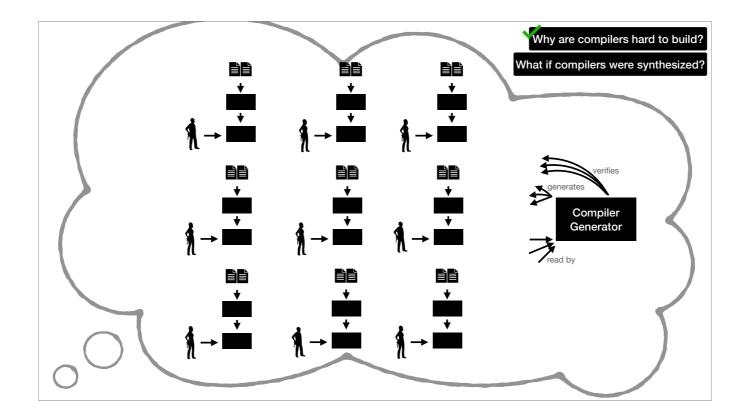

Imagine we have

[build] a hardware engineer who

[build] builds a new hardware design. If she wants to run

[build] programs on her hardware, she'll need a

[build] compiler that

[build] compiles programs to run on her design. This requires

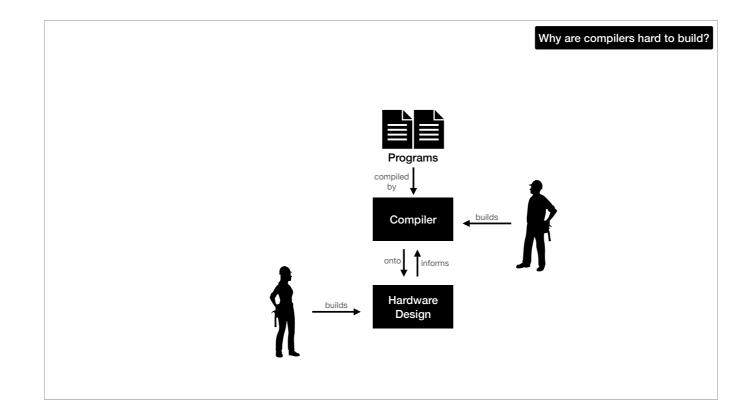

[build] a compiler engineer, who, with much time and effort

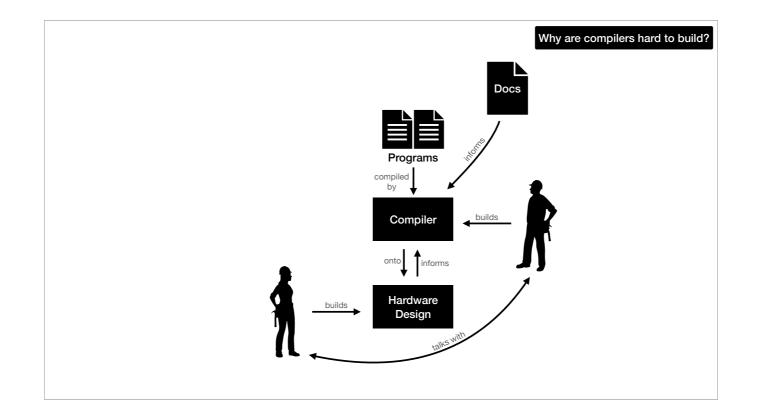

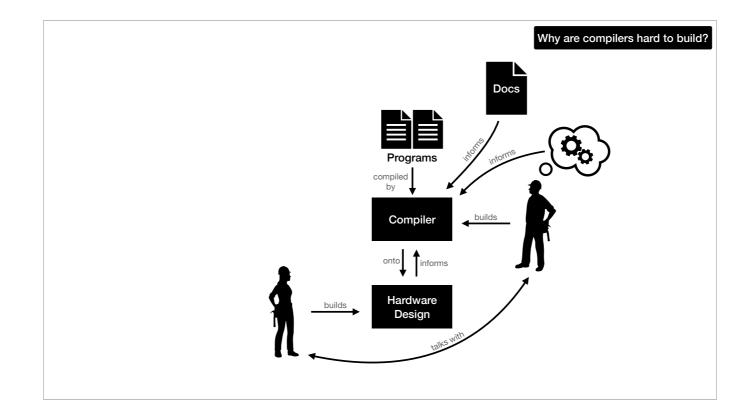

[build] builds a compiler, whose design is informed not only by

[build] the hardware design itself, but also by

[build] communications with the hardware designer,

[build] any documentation that exists for the design, and finally, by

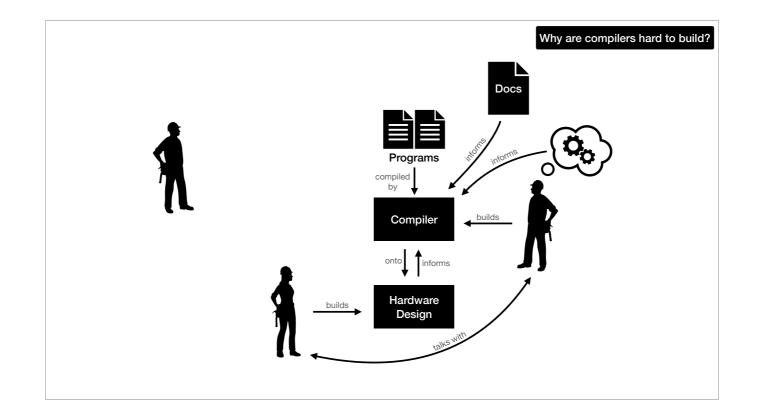

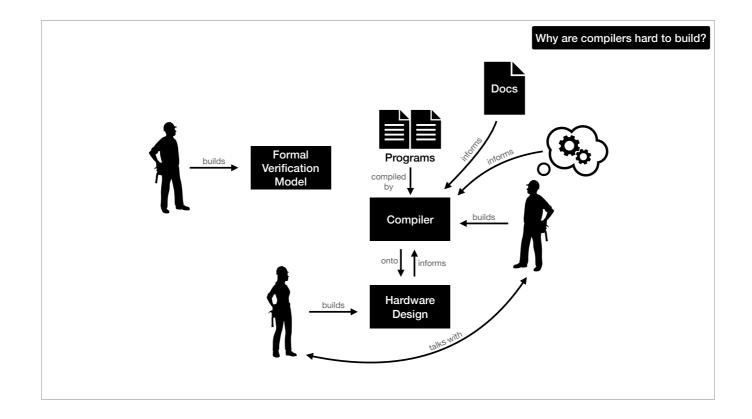

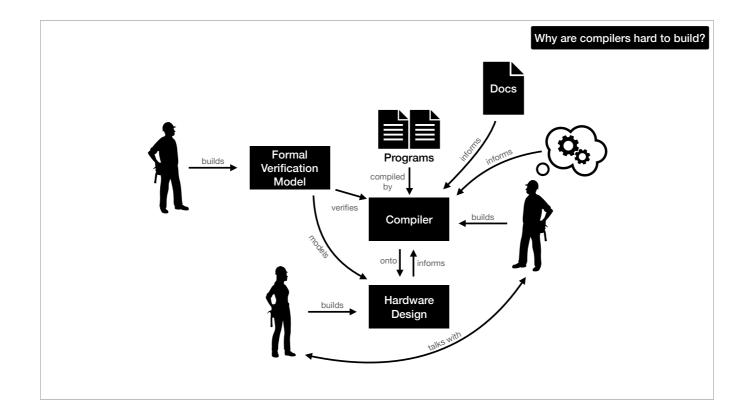

[build] the compiler engineer's own internal model of how the hardware works. If that's not confusing enough, if the team wants to ensure the compiler is correct, they'll hire

[build] a verification engineer to

[build] build a

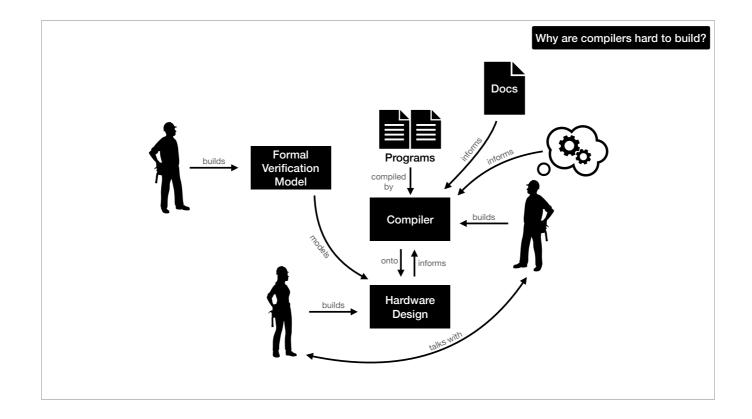

[build] formal verification model, which

[build] models the hardware and

[build] verifies that the compiler is correct. Similarly to the compiler, the design of the verification model is informed by

[build] communications with the hardware designer,

[build] the hardware design itself,

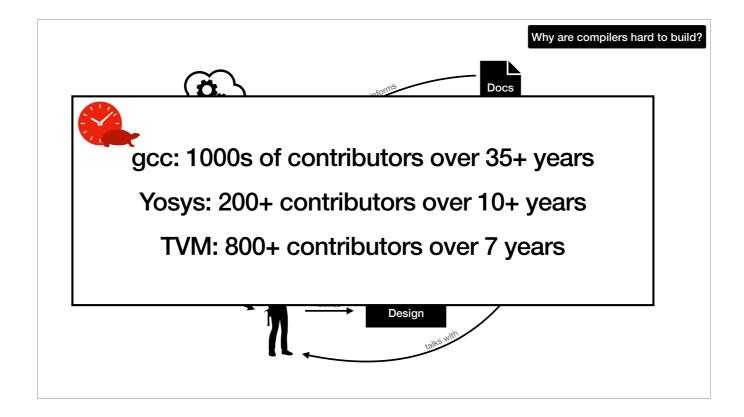

[build] the documentation, and [build] the verification engineer's own ideas about how the hardware works. [build] If this is looking a little complicated, well, I agree! But the process of building a compiler is more than just confusing; it also [build] requires significant developer effort,

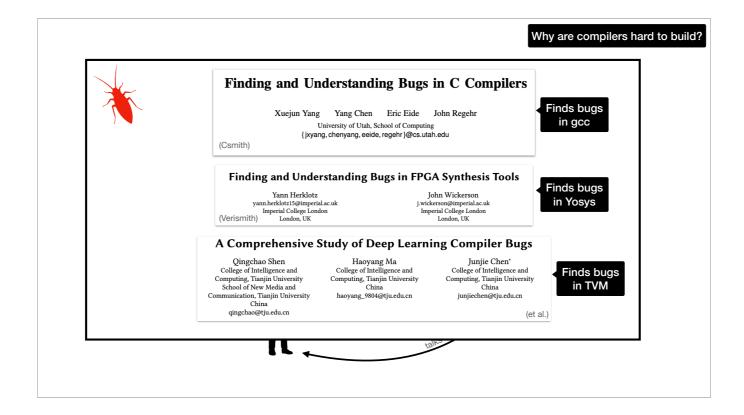

Which is clear once we see the sheer number of individual contributors and time that have gone into major open source compilers like gcc, the hardware synthesis tool Yosys, and the deep learning compiler TVM.

Furthermore, building a compiler is a [build] bug-prone process. In fact,

You can build a strong research career centered on finding and fixing bugs in these large, open-source compilers.

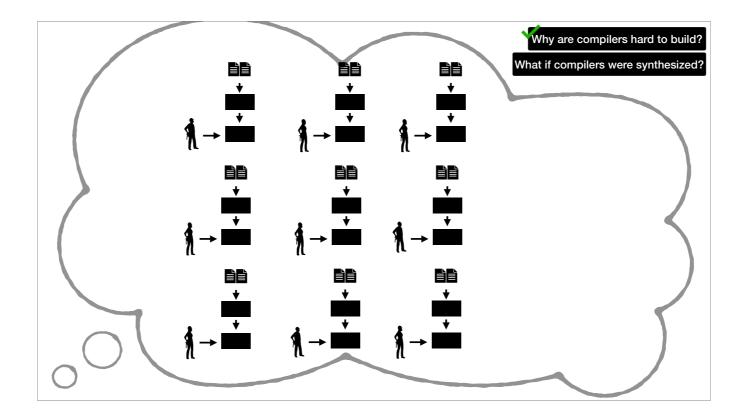

And to make matters worse, these costs are multiplicative. That is,

...for each new piece of hardware,

[build] the entire process needs to be repeated to build a new compiler. Though there exists compiler frameworks such as LLVM and MLIR which lessen the burden on compiler engineers, the process still requires significant effort and expertise.

So we asked the question ...

What we've seen is that [build] ... And, importantly, [build] ...

A natural question after all of this is [build] ...

It might sound optimistic given how much effort it is to build a compiler, but let's at least entertain the possibility.

Why are compilers hard to build?

Building a compiler requires significant engineering effort and induces numerous bugs.

## Why are compilers hard to build?

Building a compiler requires significant engineering effort and induces numerous bugs.

Those costs are multiplied with every new hardware design.

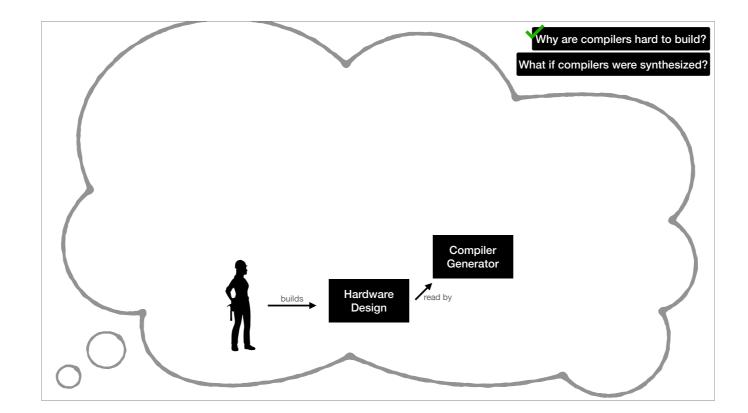

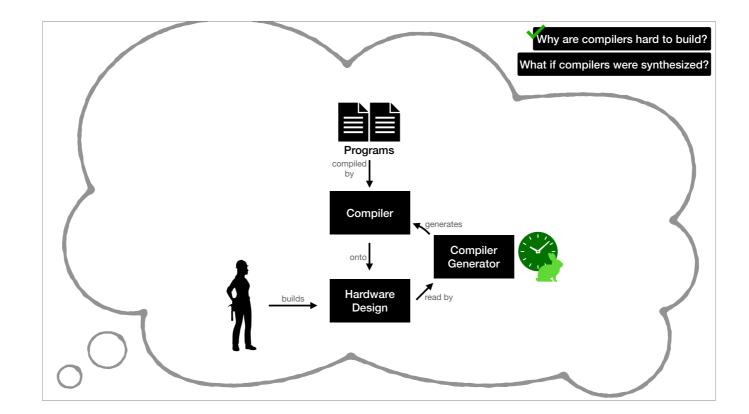

In the ideal case, our

[build] hardware designer still builds their hardware design. But now, that design is read by

[build] a compiler generator, which

[build] generates a compiler directly from their hardware implementation.

Automating compiler construction would save an immense amount of

[build] engineering effort and time.

In addition, depending on how the compiler generator is built, the generator could

[build] verify the compiler as it's being generated, producing

[build] a bug-free compiler, saving verification time and effort as well.

But best of all, this approach can scale

[build] as every new hardware design can reuse

[build] the same compiler generator, removing that multiplicative factor on effort and bugs that exists today.

In this ideal world,

[build] there is no hardware lottery, at least not because of compilers.

So we see that [build] ... [build] ... What if compilers were synthesized? Automatically generating compilers can reduce engineering effort and eliminate bugs. What if compilers were synthesized? Automatically generating compilers can reduce engineering effort and eliminate bugs. Furthermore, the approach scales with new hardware designs, thus fighting against the hardware lottery!

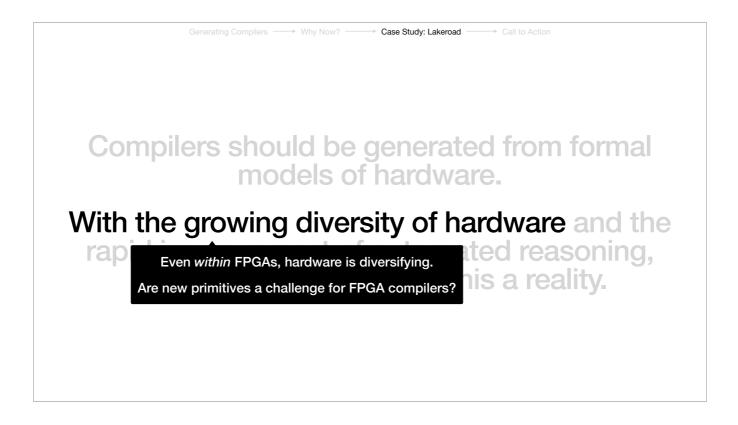

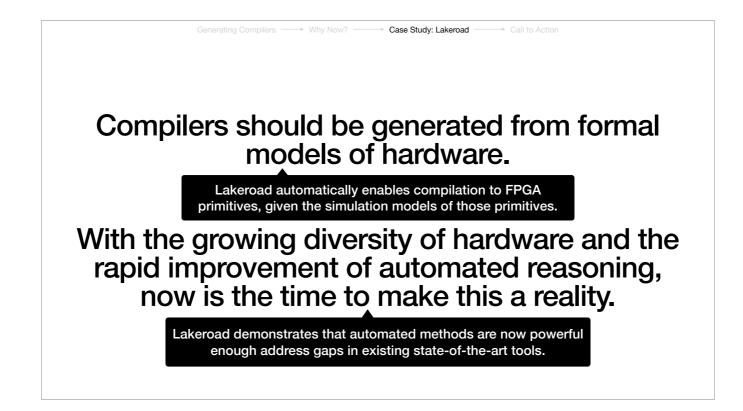

With that, I will now introduce the thesis statement of this talk, in which I claim [build] ...

Compilers should be generated from formal models of hardware.

With the growing diversity of hardware and the rapid improvement of automated reasoning, now is the time to make this a reality.

Here's our roadmap for the rest of the talk.

Let's talk about why now is the time to do this research.

We claim that, with the growing diversity of hardware and the rapid improvement of automated reasoning, now is the time to make automatic generation of compilers a reality.

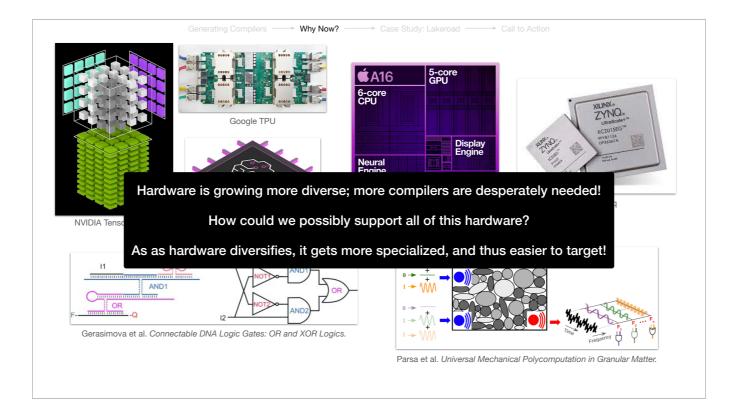

First, let's talk about what we mean by the growing diversity of hardware.

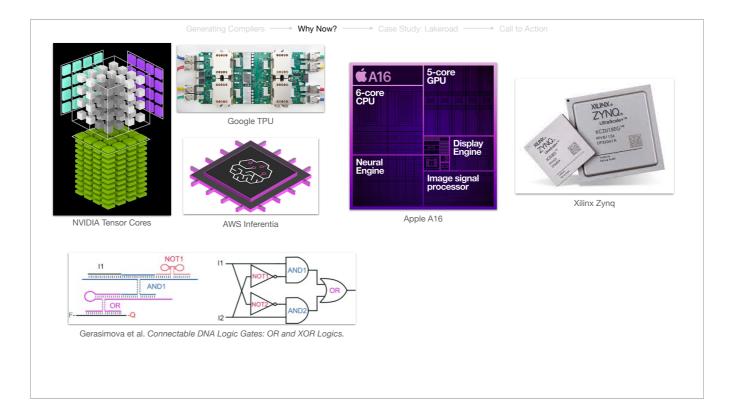

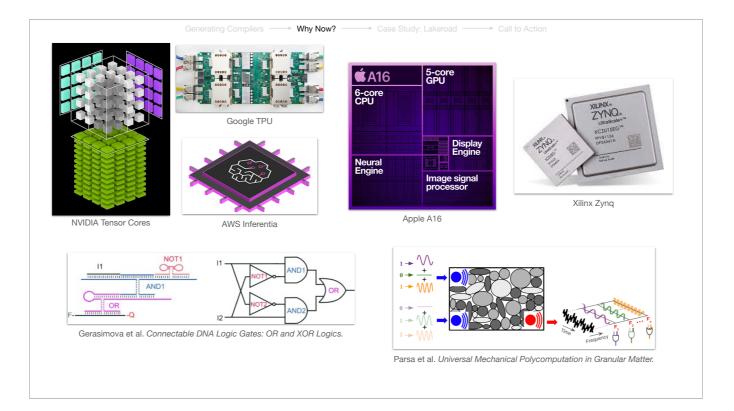

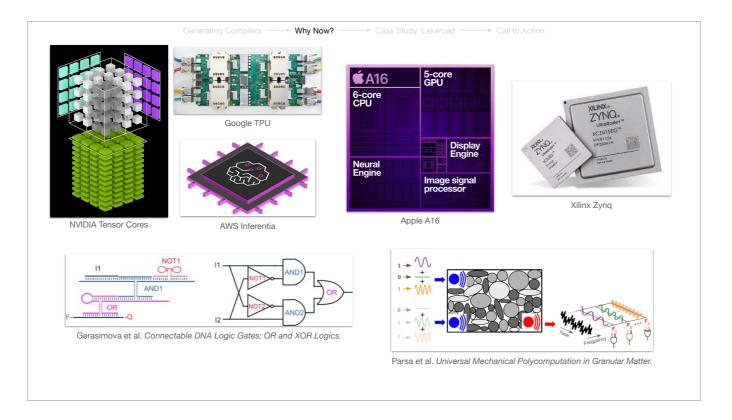

As soon as I mention the diversity of hardware, I'm sure that the first thing that pops into peoples' minds is hardware for machine learning, such as [build] GPUs and

[build] custom machine learning ASICs.

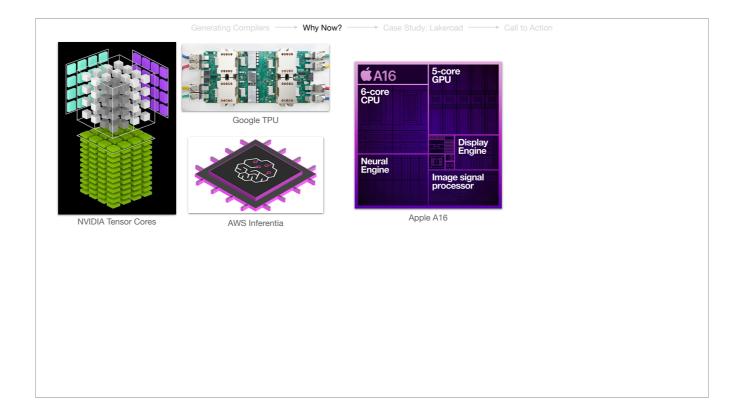

Yet even within

[build] processors like Apple's A16, we're seeing the addition of specialized accelerators like GPUs and Neural Engines.

Consider also platforms like

[build] Xilinx's Zynq chip, which includes both an ARM CPU and a reconfigurable FPGA, making quite an interesting target for compilers.

Lastly, far from the realm of silicon-based computing, people have begun computing using things like

[build] DNA strand displacement or

[build] metamaterials.

Though these are far from what we would normally consider "hardware", they require compilers nonetheless!

Given the dizzying array of hardware available today, it's clear that

[build] hardware is growing more diverse, and that compilers for new hardware are desperately needed.

This diversity can be intimidating:

[build] how could we possibly generate compilers for all of this hardware?

But the explosion of new hardware platforms actually works in our favor,

[build] because as hardware diversifies, it gets more specialized, and thus, potentially easier to target with automated methods.

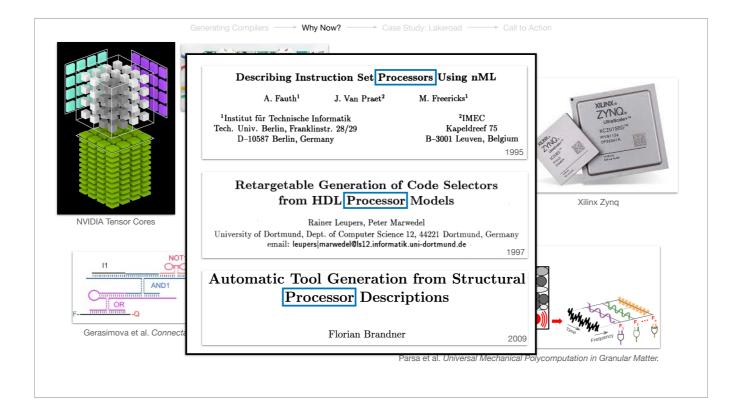

Previous work on automatically generating compilers largely focuses on

[build] processors.

Generating compilers for processors is

[build] quite a difficult task, as processors are general purpose, and compilers for general purpose processors must handle all of their capabilities.

On the other hand, all of the new hardware we're talking about is special purpose,

[build] which makes the task of reasoning about hardware's behavior much more feasible for automated methods.

But not only is our hardware more amenable to automated reasoning; our tools for automated reasoning are now powerful enough to take on the task of automated compiler generation.

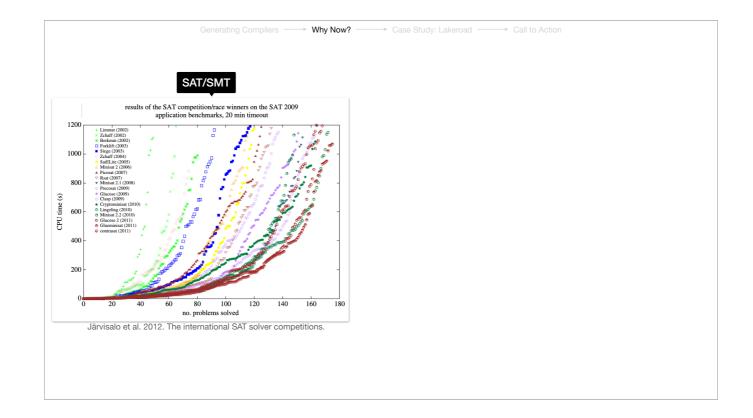

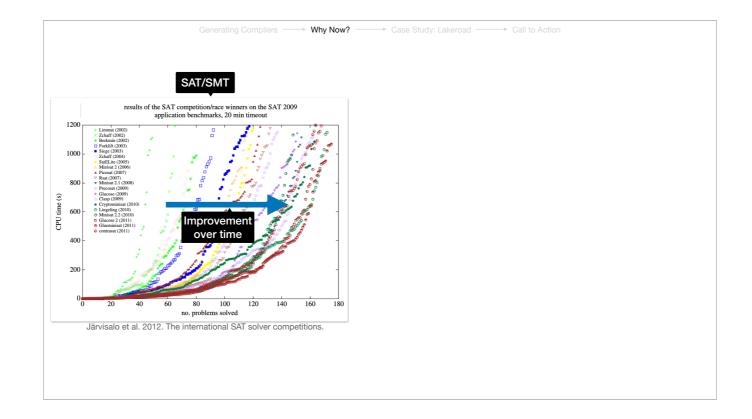

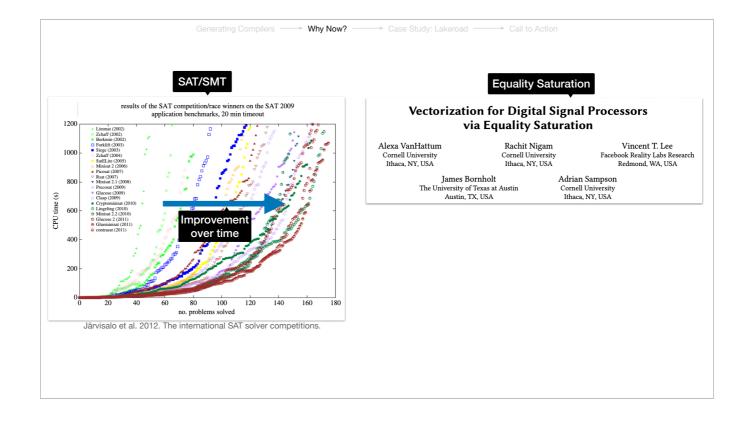

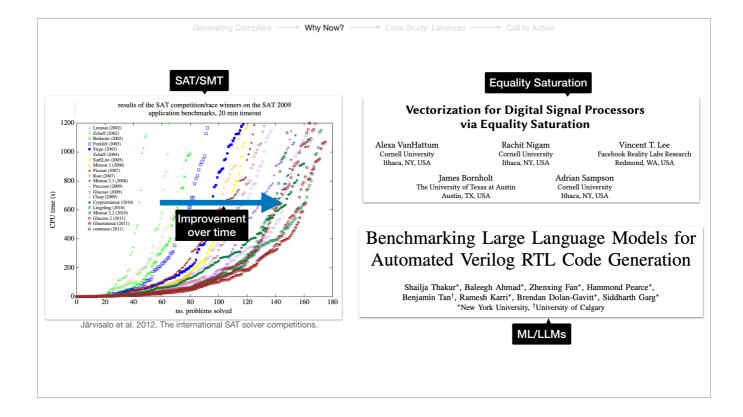

Consider, for example, [build] SAT and SMT solvers, whose performance have been [build] steadily increasing,

Or the relatively new technique of [build] equality saturation, which has already shown great promise for compiler construction,

And of course it wouldn't be a talk in 2023 if I didn't mention

[build] large language models, which are powerful tools for generating hardware code, among other tasks.

Given that this is only a small selection of the automated reasoning tools available, it's clear that [build] ...

So, why is now the time to make the automatic generation of compilers a reality? Well,

[build] ...

Furthermore,

[build] ...

Finally,

[build] ...

Now,

...let's talk about a concrete example of generating a compiler from hardware models, in a project we call Lakeroad.

We keep talking about the growing diversity of hardware platforms. Now, [build] let's look at a concrete example: FPGAs.

FPGAs are reconfigurable devices that can be used to implement hardware.

At a high level, though, you can think of an FPGA as being a bag filled with parts, or primitives.

In the past, FPGAs consisted only of

[build] lookup tables, which are primitives that can be configured to implement logic gates.

Over the years, FPGAs have added specialized primitives such as

[build] carry chains to implement fast arithmetic.

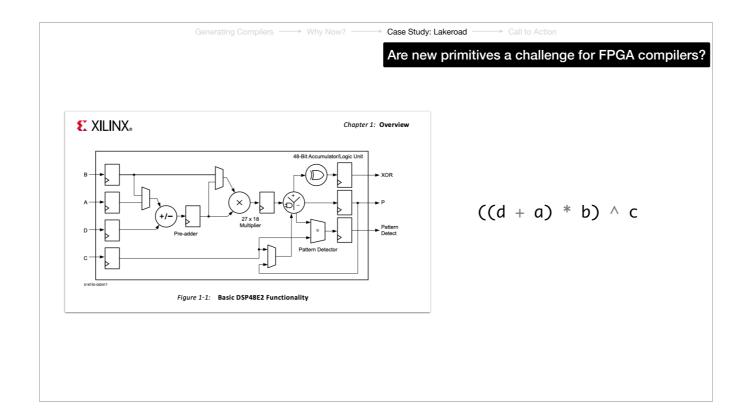

One of the most interesting and impactful additions to FPGAs has been the inclusion of

[build] digital signal processors or DSPs, which are small, programmable embedded processors.

So we can see that

[build] ...

[build] Are new primitives a challenge for FPGA compilers, as our thesis would suggest?

To test this, we will attempt to compile a simple hardware design onto a Xilinx FPGA's DSP.

In our case, our simple design takes four inputs and computes this expression in three pipeline stages.

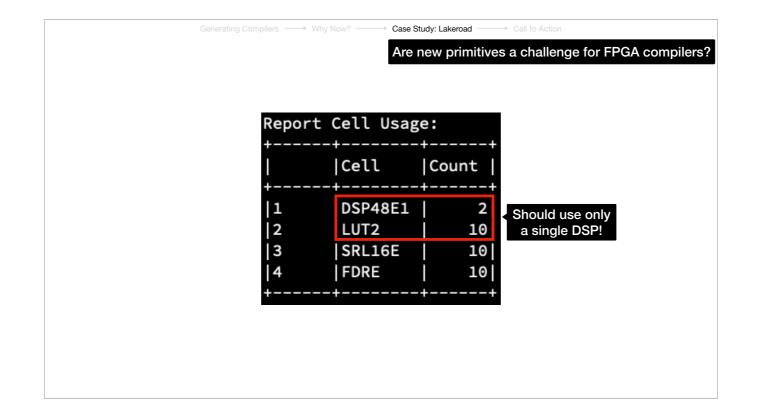

The Xilinx DSP documentation claims that this expression is supported on the DSP. But when we attempt to compile our design using the state of the art compiler for Xilinx FPGAs, we see a surprising result.

| Generating Compilers | → Why Now?> Ca | se Study: Lakeroad | → Call to Action                  |

|----------------------|----------------|--------------------|-----------------------------------|

|                      | A              | re new primitive   | s a challenge for FPGA compilers? |

|                      | _              |                    |                                   |

|                      |                |                    |                                   |

| Repo                 | ort Cell Us    | age:               |                                   |

| +                    | +              | ++                 |                                   |

|                      | Cell           | Count              |                                   |

| +                    | +              | ++                 |                                   |

| 1                    | DSP48E         | 1   2              |                                   |

| 2                    | LUT2           | 10                 |                                   |

| 3                    | SRL16E         | 10                 |                                   |

| 4                    | FDRE           | 10                 |                                   |

| +                    | +              | ++                 |                                   |

|                      |                |                    | -                                 |

|                      |                |                    |                                   |

|                      |                |                    |                                   |

|                      |                |                    |                                   |

|                      |                |                    |                                   |

We see that the design is in fact compiled onto DSPs; but instead of [build] using a single DSP as expected, it uses two DSPs and ten look up tables.

So, are new primitives...

From our brief experiment, it seems like the answer is [build] yes! [build] But this is unsurprising...

Generating Compilers ------> Why Now? ------> Case Study: Lakeroad ------> Call to Action

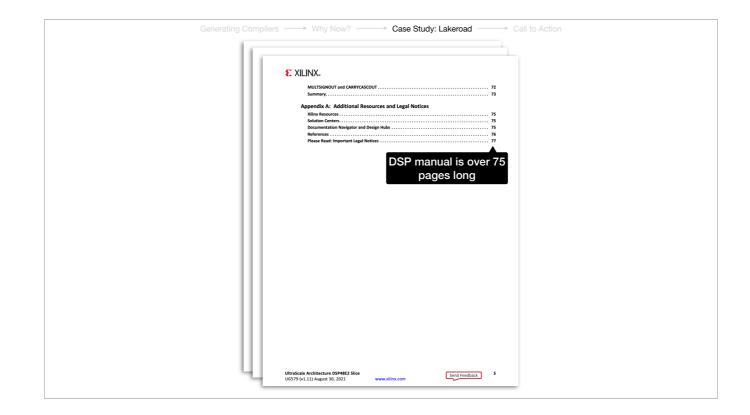

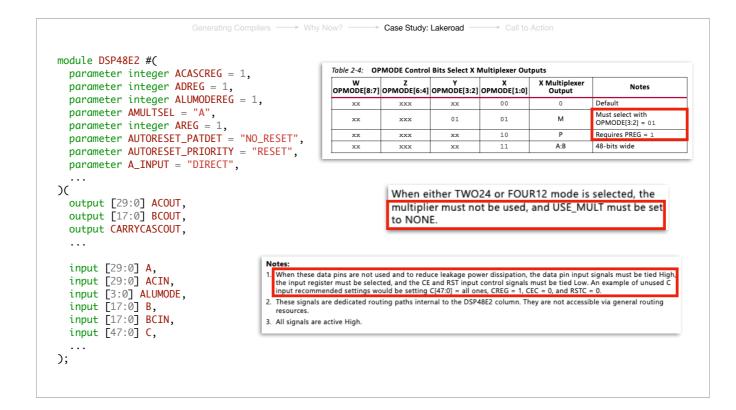

The manual for our Xilinx DSP alone is [build] over 75 pages long.

Furthermore, instantiating a DSP requires

[build] setting over 100 ports and parameters, while

[build] obeying strict requirements on port and parameter values, described throughout the 75 page manual.

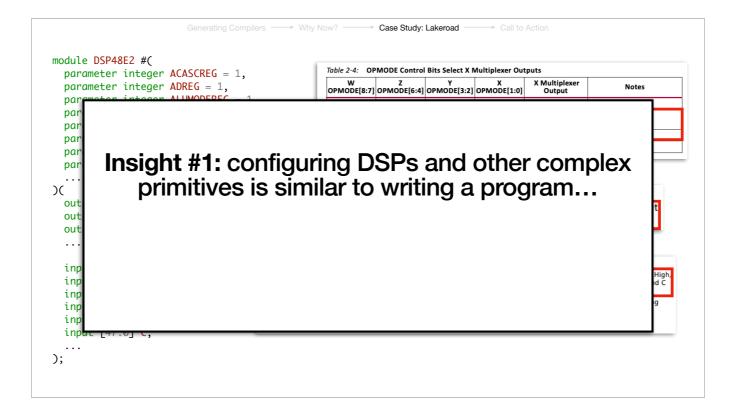

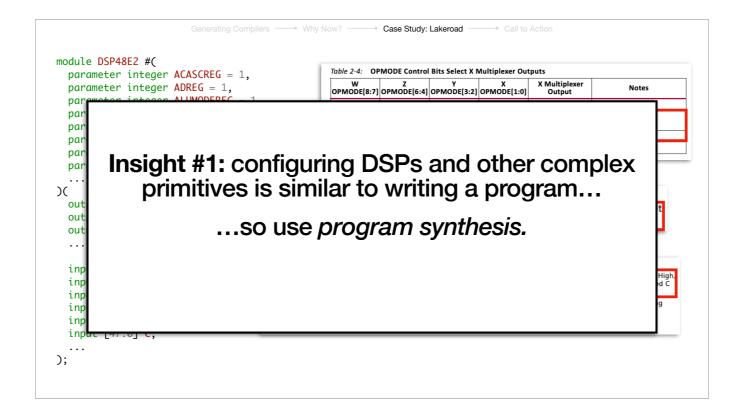

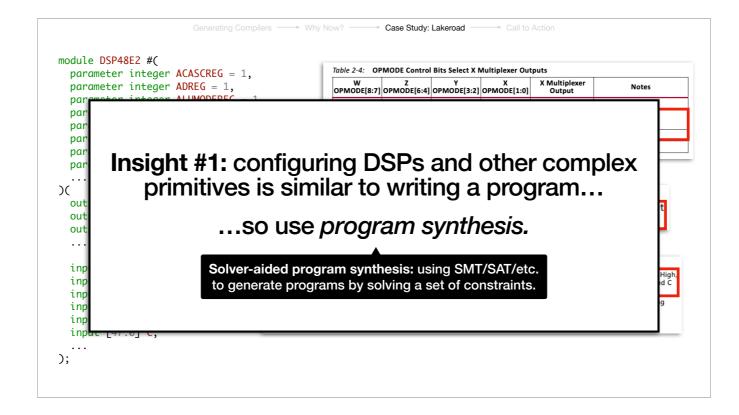

With all of these complex interdependencies on what values are legal for which parameters based on the values of other parameters, [build] configuring a DSP is starting to sound a lot like writing a program.

| parameter integer ACASCREC                                                                        | i = 1,                                                                                                                        | -                                                                         |                    |                                                                          | Multiplexer Out                                         | -                                                                         |                                      |

|---------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|--------------------|--------------------------------------------------------------------------|---------------------------------------------------------|---------------------------------------------------------------------------|--------------------------------------|

| parameter integer ADREG =                                                                         |                                                                                                                               | W<br>OPMODE[8:7]                                                          | Z<br>OPMODE[6:4]   | Y<br>OPMODE[3:2]                                                         | X<br>OPMODE[1:0]                                        | X Multiplexer<br>Output                                                   | Notes                                |

| parameter integer ALUMODER                                                                        | REG = 1,                                                                                                                      | xx                                                                        | ххх                | хх                                                                       | 00                                                      | 0                                                                         | Default                              |

| <pre>parameter AMULTSEL = "A", parameter integer AREG = 1</pre>                                   |                                                                                                                               | xx                                                                        | xxx                | 01                                                                       | 01                                                      | М                                                                         | Must select with<br>OPMODE[3:2] = 01 |

| parameter AUTORESET_PATDET                                                                        |                                                                                                                               | xx                                                                        | xxx                | xx                                                                       | 10                                                      | Р                                                                         | Requires PREG = 1                    |

| parameter AUTORESET_PRIORI                                                                        |                                                                                                                               | xx                                                                        | xxx                | xx                                                                       | 11                                                      | A:B                                                                       | 48-bits wide                         |

| output [29:0] ACOUT,                                                                              | Configuring the Da<br>equires setting 10<br>orts and paramet                                                                  | -00                                                                       | _                  | er must no                                                               |                                                         |                                                                           | selected, the<br>JLT must be set     |

| C<br>output [29:0] ACOUT,<br>output [17:0] BCOUT,<br>output CARRYCASCOUT,<br>Output CARRYCASCOUT, | Configuring the D<br>equires setting 10                                                                                       | -00                                                                       | multipli           | er must no                                                               |                                                         |                                                                           |                                      |

| (<br>output [29:0] ACOUT,<br>output [17:0] BCOUT,<br>output CARRYCASCOUT,                         | Configuring the D<br>equires setting 10<br>orts and paramet<br>Notes:<br>1. When these da<br>the input regis<br>input recomme | 00+<br>ers<br>ta pins are not u<br>ter must be selec<br>ended settings we | multipli<br>to NON | er must no<br>E.<br>uce leakage pov<br>and RST input<br>C[47:0] = all or | ver dissipation,<br>control signals<br>ies, CREG = 1, C | and USE_MU<br>the data pin input<br>must be tied Low.<br>EC = 0, and RSTC | JLT must be set                      |

| parameter integer ACASCREG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | = 1,                                                                                                                           | Table 2-4: OF                                                                             | MODE Contro        | Bits Select X M                                                          | Multiplexer Out                                         | puts                                                                      |                                      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|--------------------|--------------------------------------------------------------------------|---------------------------------------------------------|---------------------------------------------------------------------------|--------------------------------------|

| parameter integer $ADREG = 1$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ,                                                                                                                              | W<br>OPMODE[8:7]                                                                          | Z<br>OPMODE[6:4]   | Y<br>OPMODE[3:2]                                                         | X<br>OPMODE[1:0]                                        | X Multiplexer<br>Output                                                   | Notes                                |

| parameter integer ALUMODERE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | G = 1,                                                                                                                         | xx                                                                                        | ххх                | xx                                                                       | 00                                                      | 0                                                                         | Default                              |

| <pre>parameter AMULTSEL = "A",<br/>parameter integer AREG = 1,</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                | xx                                                                                        | xxx                | 01                                                                       | 01                                                      | м                                                                         | Must select with<br>OPMODE[3:2] = 01 |

| parameter AUTORESET_PATDET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                | xx                                                                                        | ххх                | xx                                                                       | 10                                                      | Р                                                                         | Requires PREG = 1                    |

| parameter AUTORESET_PRIORIT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | · · ·                                                                                                                          | xx                                                                                        | xxx                | xx                                                                       | 11                                                      | A:B                                                                       | 48-bits wide                         |

| output [29:0] ACOUT, rec                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ",<br>onfiguring the DS<br>quires setting 10<br>rts and paramete                                                               | 0+                                                                                        | _                  | er must no                                                               |                                                         |                                                                           | selected, the<br>JLT must be set     |

| Contraction (Contraction) (Con | onfiguring the DS<br>quires setting 10<br>rts and paramete                                                                     | 0+<br>ers                                                                                 | multipli<br>to NON | er must no<br>E.                                                         | ot be used,                                             | and USE_MU                                                                | JLT must be set                      |

| Coutput [29:0] ACOUT,<br>output [17:0] BCOUT,<br>output CARRYCASCOUT,<br><br>input [29:0] A,<br>input [29:0] ACIN,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | onfiguring the DS<br>quires setting 10<br>rts and paramete<br>Notes:<br>1. When these dat<br>the input regist                  | 0+<br>ers                                                                                 | multipli<br>to NON | er must no<br>E.                                                         | ver dissipation,<br>control signals                     | and USE_MU                                                                | JLT must be set                      |

| output [29:0] ACOUT,<br>output [17:0] BCOUT,<br>output CARRYCASCOUT,<br><br>input [29:0] A,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | onfiguring the DS<br>quires setting 10<br>rts and paramete<br>Notes:<br>1. When these dat<br>the input regist<br>input recomme | 0+<br>ers<br>a pins are not u<br>er must be selec<br>nded settings wo<br>re dedicated rou | multipli<br>to NON | er must no<br>E.<br>uce leakage pov<br>and RST input<br>C[47:0] = all on | ver dissipation,<br>control signals<br>ies, CREG = 1, C | and USE_MU<br>the data pin input<br>must be tied Low.<br>EC = 0, and RSTC | JLT must be set                      |

Our first insight is that...

[build] so why not use program synthesis?

For those unfamiliar with program synthesis, I won't go into too much detail, but just know that [build] *solver aided program synthesis* is the process of...

Because configuring DSPs is so complicated, Xilinx provides...

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | );                                                                                                           | assign CECARRYIN_in = (CECARRYIN !== 1'bx) && CECARRYIN; // rv                                                 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|

| DSP48E2.v                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | // define constants                                                                                          | θ<br>assign CECTRL_in = (CECTRL !== 1'bx) && CECTRL; // rv θ                                                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | localparam MODULE_NAME = "DSP48E2";                                                                          | assign CEC_in = (CEC !== 1'bx) && CEC; // rv 0                                                                 |

| paran                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                              | assign CED_in = (CED !== 1'bx) && CED; // rv 0                                                                 |

| // Convright (c) 1995/2017 Viliny Toc                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | <pre>// Parameter encodings and registers</pre>                                                              | assign CEINMODE_in = CEINMODE;                                                                                 |

| paran // All Right Reserved.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | localparam AMULTSEL_A = 0;                                                                                   | assign CEM_in = (CEM !== 1'bx) && CEM; // rv 0                                                                 |

| paran///                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | <pre>localparam AMULTSEL_AD = 1;</pre>                                                                       | assign CEP_in = (CEP !== 1'bx) && CEP; // rv 0                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | <pre>localparam AUTORESET_PATDET_NO_RESET = 0;</pre>                                                         | assign CLK_in = (CLK !== 1'bx) && (CLK ^ IS_CLK_INVERTED_REG);                                                 |

| paran// / // / Vendor : Xilinx                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | `endif                                                                                                       | // rv 0<br>assign C_in[0] = (C[0] === 1'bx)    C[0]; // rv 1                                                   |

| // \ \ \/ Version : 2017.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                              | assign C_in[10] = (C[10] === 1'bx)    C[10]; // rv 1                                                           |

| Daran // \ Description : Xilinx Unified Simulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                              | а                                                                                                              |

| // / / 48-bit Multi-Functional                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | assign ACIN_in = ACIN;                                                                                       | assign D_in[1] = (D[1] !== 1'bx) && D[1]; // rv θ                                                              |